OR-AND-Invert

| Gatter-Typen | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

| AOI | |

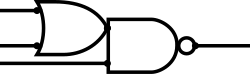

OR-AND-Invert-Gatter (abgekürzt OAI-Gatter) sind eine Kombination von Logikgattern, die aus einem oder mehreren ODER-Gattern gefolgt von einem NAND-Gatter bestehen. Sie lassen sich in Logikfamilien wie CMOS oder TTL mit wenig Aufwand als gemischtes Gatter realisieren.[1] Sie sind dual zu den AND-OR-Invert-Gattern.

Übersicht

Die mit einem OAI-Gatter realisierte Funktion entspricht der negierten Product-of-Sums-Formulierung von booleschen Funktionen. Gruppen mit , Eingangssignalen werden mit ODER verknüpft. Diese Werte werden dann mit einem NAND-Gatter mit Eingängen verknüpft.

Beispiele – 2-1 OAI-Gatter

Das ODER-Gatter hat die Eingänge A und B.

Ein 2-1 OAI-Gatter realisiert die Funktion

mit der Wahrheitstabelle

| Wahrheitstabelle 2-1 OAI | |||

| Eingang A B C |

Ausgang Y | ||

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

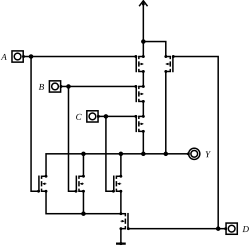

Realisierung CMOS

OAI-Gatter können in CMOS effizient als gemischte Gatter implementiert werden. Ein Beispiel zeigt die folgende Abbildung.[2]

Weblinks

Einzelnachweise

- ↑ P. Fischer: Aussagenlogik und Gatter. (PDF) Universität Heidelberg, abgerufen am 21. Januar 2024.

- ↑ Norman Hendrichs: CMOS OAI31 or-and-invert complex gate. Universität Hamburg, abgerufen am 12. Februar 2024.